## DOCTORAL THESIS

# On Data Structures and Memory Models

Johan Karlsson

Luleå University of Technology Department of Computer Science and Electrical Engineering

2006:24 | ISSN: 1402-1544 | ISRN: LTU-DT -- 06/24 -- SE

## On Data Structures and Memory Models

by

Johan Karlsson

Department of Computer Science and Electrical Engineering Luleå University of Technology SE-971 87 Luleå, Sweden

$\mathrm{May}\ 2006$

#### Supervisor

Andrej Brodnik, Ph.D., Luleå University of Technology, Sweden

### Abstract

In this thesis we study the limitations of data structures and how they can be overcome through careful consideration of the used memory models. The word RAM model represents the memory as a finite set of registers consisting of a constant number of unique bits. From a hardware point of view it is not necessary to arrange the memory as in the word RAM memory model. However, it is the arrangement used in computer hardware today.

Registers may in fact share bits, or overlap their bytes, as in the *RAM* with Byte Overlap (RAMBO) model. This actually means that a physical bit can appear in several registers or even in several positions within one register. The RAMBO model of computation gives us a huge variety of memory topologies/models depending on the appearance sets of the bits.

We show that it is feasible to implement, in hardware, other memory models than the word RAM memory model. We do this by implementing a RAMBO variant on a memory board for the PC100 memory bus. When alternative memory models are allowed, it is possible to solve a number of problems more efficiently than under the word RAM memory model. We look at three priority queue related problems: the *Discrete Extended Priority Queue*, the *Time Queue*, and the *Prefix Sum* problems.

We side-step several lower bounds for the discrete extended priority queue problem and the prefix sum problem by allowing alternative memory models. We suggest two data structures and algorithms, which provide all the operations for the two problems in worst case constant time. It is not possible to achieve this time bound using the word RAM memory model.

We also suggest a data structure for the time queue problem. The algorithms run in expected constant time for the operations that delete the minimum element and worst case constant time for the other operations. The data structure can be maintained by several processes that share a part of the memory. Finally, we also show that it is possible to replace the ALU in a processor with memory while still keeping the ALUs functionality. Hence it is well worth and practical to consider alternative memory models, at least for special purpose processors.

iv Abstract

## Acknowledgments

First I would like to thank my supervisor Dr. Andrej Brodnik for all his encouragement, guidance, and friendship and for the many discussions over the last years. I would also like to thank Prof. Svante Carlsson and Dr. Jingsen Chen who first introduced the field of theoretical computer science to me and accepted me as a Ph.D. student.

Thanks also to Prof. J. Ian Munro who invited me to spend seven months at University of Waterloo under his guidance. The time there where a great source of inspiration to continue with my studies. It was also an opportunity, for my fiancée and me, to learn more about the life in Canada. Wendy, thank you for helping us with all practical things when we where there.

All colleges and friends, both at the university and outside, thank you for lighting up my days with 'fika', pool, frisbee golf, swimming, long chats about everything and nothing, coffee, single malts, ...

My family has always encouraged me to study, thanks. Finally, I would like to thank my fiancée Christina for all her love, support, and patience and my son Simon who always greets me with a smile on his face when I come home.

vi Acknowledgments

## Contents

| Abstr         | act                                                                                | iii          |

|---------------|------------------------------------------------------------------------------------|--------------|

| Ackno         | owledgments                                                                        | $\mathbf{v}$ |

| Includ        | led Papers                                                                         | ix           |

| Introd  1 2   | Models of Computation and Memory Models                                            | 1<br>1<br>2  |

| $\frac{3}{4}$ | 2.1 Priority Queues and Related Data Structures Summary of Included Papers         | 3<br>5<br>7  |

| Paper         | $\mathbf{s}$                                                                       | 13           |

| 1             | Design of a High Performance Memory Module on PC100 $$                             | 15           |

| 2             | Bitwise Operations under RAMBO                                                     | 25           |

| 3             | Multiprocess Time Queue                                                            | 41           |

| 4             | Worst Case Constant Time Priority Queue                                            | 63           |

| 5             | An O(1) Solution to the Prefix Sum Problem on a Specialized<br>Memory Architecture | 79           |

viii Contents

## Included Papers

The following papers are included in this thesis:

#### • Paper 1

Roni Leben, Marijan Miletić, Marjan Špegel, Andrej Trost, Andrej Brodnik and Johan Karlsson, Design of a High Performance Memory Module on PC100. In Proceedings Electrotechnical and Computer Science Conference, Slovenia, 1999.

#### • Paper 2

Andrej Brodnik and Johan Karlsson. *Bitwise Operations under RAMBO*. Research report LTU-FR--06/12--SE, Luleå University of Technology, Luleå, Sweden, May 2006. http://epubl.luth.se/1402-1528/2006/12/index.html.

#### • Paper 3

Andrej Brodnik and Johan Karlsson, Multiprocess Time Queue. In Peter Eades and Tadao Takaoka, editors, Algorithms and Computation ISAAC 2001, 12th International Symposium, volume 2223 of Lecture Notes in Computer Science, pages 599–609. Springer, December 2001.

#### • Paper 4

Andrej Brodnik, Svante Carlsson, Michael L. Fredman, Johan Karlsson and J. Ian Munro, Worst Case Constant Time Priority Queue. In Journal of System and Software, 78(3):249-256, December 2005.

#### • Paper 5

Andrej Brodnik, Johan Karlsson, J. Ian Munro and Andreas Nilsson, An O(1) Solution to the Prefix Sum Problem on a Specialized Memory Architecture. In IFIP 19th World Computer Congress, TC1 4th International Conference on Theoretical Computer Science, Springer, 2006.

x Included Papers

In this thesis we study the limitations of data structures and how they can be overcome through careful consideration of the used memory model. The main question is whether one should consider alternative memory models when designing data structures or only work with the already established ordinary RAM memory model.

The thesis consists of two parts, this introduction and five research papers. We start the introduction with a brief discussion about models of computation and memory models. This is followed by a discussion about data structures in general and data structures used to solve priority queue related problems in particular. The five papers are then summarized. We end the introduction with some conclusions and open research questions.

#### 1 Models of Computation and Memory Models

A computer today consists of a CPU, memory, and an I/O subsystem. The CPU contains, at least, a control unit, a cache, and an Arithmetic Logic Unit (ALU). The ALU is used to compute various functions. These functions usually include the bitwise operations (boolean operations and various shifts) and arithmetic operations (addition, subtraction, multiplication, and division). Such a computer is called a von Neumann computer [29] and is modeled as a Random Access Machine (RAM) [8, 26]. In the RAM model, the CPU can perform four types of operations: I/O operations which let the computer communicate with its surrounding, read and write operations which move data from and to the memory, jump operations (conditional or unconditional) which affect the flow of control, and arithmetic and logic operations.

Depending on which arithmetic and logic operations one allows, we talk about different variants of the RAM model. The basic RAM model allows addition and subtraction. If multiplication and division are allowed we denote the model MRAM and if bitwise boolean operations are allowed we use an additional B in the name (for example BRAM and MBRAM) [26].

In the RAM models, the memory is modeled as an infinite set of registers, which store values. This is not feasible since it would require an infinite address size and consequently an infinite register size to address them. Further, if we allow multiplication and an unbounded word size the RAM model becomes as powerful as the parallel model PRAM [15, 17, 23]. Hence we restrict the word size and use w to denote it. Such RAMs are denoted w ord RAMs. A restricted word size implies a bounded universe and without loss of generality we let the universe be the integers from 0 to M-1 where  $M \leq 2^w$ . In this thesis we only consider word RAMs and we specify the set of operations on a case-by-case basis.

Moreover, in the RAM models, each register is represented by individual bits. In the word RAM models there are  $2^w$  registers consisting of w bits and hence in total there are  $2^w \cdot w$  bits in the memory. We refer to this memory model as the RAM memory model. From a hardware point of view it is not necessary to arrange the memory as in the RAM memory model. However, it is the arrangement used in computer hardware today.

Fredman and Saks suggested that registers may share bits, or in their words "words that overlap", and they named the model of computation: RAM with Byte Overlap (RAMBO) [11]. This actually means that a physical bit can appear in several registers or even in several positions within one register. Brodnik formalized the definition and introduced the notion of an implicit and an explicit RAMBO [4]. Each individual bit appears in the registers according to its appearance set. In the implicit RAMBO the appearance sets are static, and in the explicit RAMBO they are dynamic, that is, the appearance sets can be changed during execution of a program. The RAMBO model of computation gives us a huge variety of memory models depending on the appearance sets of the bits. Note that one part of the memory can have bytes that overlap while another does not.

#### 2 Data Structures

Data structures are used by most computer programs to organize their data so that they can be processed efficiently. Several different data structures can often be used to solve one particular problem. For example, to store a set of elements one can use, among other data structures, a linked list, an array, or a hash table. Depending on the properties of the set and how it will be processed, different properties of the data structures are important.

We will look at a few data structures that can be used to solve priority queue related problems. These data structures can be used more efficiently if stored in alternative memory models.

#### 2.1 Priority Queues and Related Data Structures

Priority queues and variants thereof are used to solve a variety of problems: sorting, event driven simulation, time-out managers, dictionaries, union-split-find, graph problems (for example shortest path and minimum spanning tree), closest neighbour searches, scheduling, etc. [7, 9, 18, 22, 25]. These problems appear in many applications, for example: routing of internet traffic (IP address lookup), 3-D games, spread sheet programs, and travel planning.

We look at two variants of priority queues; the *Discrete Extended Priority Queue*, and the *Time Queue*. The time queue is targeted at solving the problem of supporting a time-out manager while the discrete extended priority queue is more general and can be used in solutions to all of the above stated problems. Further, we also look at the related *Prefix Sum* problem introduced by Fredman [10].

The discrete extended priority queue is a rather general extension of the priority queue, which in its most basic variant only supports the operations insert, min, and deleteMin.

**Definition 1** The Discrete Extended Priority Queue problem is to maintain a set  $\mathcal{N}$  of size N with elements drawn from an ordered bounded universe  $\mathcal{M} = [0..M-1]$  and support the following operations:

```

\mathcal{N} := \mathcal{N} \cup \{e\},\

insert(e)

\mathcal{N} := \mathcal{N} \setminus \{e\},\

delete(e)

return the largest element f \in \mathcal{N} such that f < e,

predecessor(e)

successor(e)

return the smallest element f \in \mathcal{N} such that f > e,

member(e)

return whether e \in \mathcal{N},

return the smallest element of \mathcal{N},

min()

return the largest element of \mathcal{N},

max()

delete the smallest element of \mathcal{N},

deleteMin()

deleteMax()

delete the largest element of \mathcal{N}.

```

Note that using the first four operations the last five can be supported. The min() operation is a special case of successor(e) and max() of predecessor(e) while deleteMin() and deleteMax() are special cases of delete(e). The member(e) operation is equivalent to checking if successor(predecessor(e)) is equal to e.

Under the pointer machine model (cf. [21]), Mehlhorn et al. [18] proved a lower bound of  $\Omega(\lg\lg M)$  for the discrete extended priority queue problem. The stratified tree by van Emde Boas et al. provides a matching upper bound [25]. Beame and Fich later gave a lower bound for the predecessor query under the communication game model (cf. [19, 30]). Under the cell probe model (cf. [32]) the lower bound becomes  $\Omega(\min((\lg\lg M/\lg\lg\lg M), \sqrt{\lg N/\lg\lg N}))$  when restricting the memory usage to  $N^{O(1)}$  words, which also applies to the RAM models [3]. They also gave a matching upper bound, in the RAM model and hence the communication game and the cell probe models, for the static version of the problem (without insert, delete, deleteMin and deleteMax). Andersson and Thorup [2] gave a data structure and an algorithm with  $O(\sqrt{\lg N/\lg \lg N})$

worst case time for the dynamic version. For the static general case (arbitrary number of dimensions), Brodnik and Munro [6] gave a data structure with O(1) worst case time for any N but using O(M) bits of space. On the other hand, Ajtai et al. [1] presented a solution using only O(N) words when  $N = O(M^{1/p})$ .

The next problem we look at is to support a time-out manager, which associates items with time stamps. The manager also has a current time, which is increased. If it is increased to the time stamp of some item, this item is considered to have timed out and should be handled specially. Usually the current time is increased according to a real time clock. The operations of the time queue are chosen to support the time-out manager:

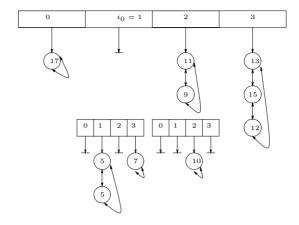

**Definition 2** The Time Queue problem is the problem of maintaining a set  $\mathcal{N}$  of elements and to support the following operations (where  $t_0$  is the time of the min element and C is the maximum duration of any element):

```

\begin{array}{ll} \text{insert}(e,\ t) & \text{iff } t_0 < t \leq t_0 + C \ \text{then let } \mathcal{N} := \mathcal{N} \cup \{e\} \ \text{with } e.t = t, \\ \text{delete}(e) & \text{let } \mathcal{N} := \mathcal{N} \setminus \{e\}, \\ \text{min}() : e & \text{return the min element,} \\ \text{deleteMin}() & \text{delete the min element,} \\ \text{update}(e,t) & \text{iff } t_0 < t \leq t_0 + C \ \text{then change the time } e.t \ \text{of } e \ \text{to } t, \\ \text{deltessThan}(t,\ \mathcal{F}) & \text{delete all elements } e \ \text{with time } e.t \ \text{less than } t \ \text{and } call \\ & \text{the function '$\mathcal{F}$' for each of the deleted elements.} \end{array}

```

Any solution to the discrete extended priority queue problem can be use to solve the time queue problem. In addition, Brown [7] suggested the use of a data structure called *Calendar Queue* and Varghese and Lauck [28] suggested a very similar solution called *Hashed and Hierarchical Timing Wheel*.

We consider a variation of the time queue problem where two processes must be able to use the data structure (cf. [12, 17, 23, 24]). One process performs time critical tasks and must be guaranteed constant time operations. This process, however, only needs to perform the min operation and a restricted update operation. The other process performs all operations and may spend more time on each operation.

The last problem we study is the prefix sum problem, which was introduced by Fredman [10]:

**Definition 3** The Prefix Sum problem is to maintain an array  $\mathcal{A}$  of size N and to support the following operations (where  $0 \le j < N$ ):

```

update(j, \Delta) \mathcal{A}(j) := \mathcal{A}(j) + \Delta, retrieve(j) return \sum_{i=0}^{j} \mathcal{A}(i).

```

A solution to the prefix sum problem also gives a solution to the Rank problem;

**Definition 4** The Rank problem is to maintain a set  $\mathcal{N}$  of size N with elements drawn from an ordered bounded universe  $\mathcal{M} = [0..M-1]$  and support the following operations:

```

\begin{array}{ll} \texttt{insert}(e) & \mathcal{N} := \mathcal{N} \cup \{e\}. \\ \texttt{delete}(e) & \mathcal{N} := \mathcal{N} \backslash \{e\}, \\ \texttt{rank}(e) & \textit{return the number of elements } f \in \mathcal{N} \textit{ where } f \leq e. \end{array}

```

INTRODUCTION 5

In an array A of size M we let the value of A[i] be 1 if  $i \in \mathcal{N}$  and 0 otherwise. Now the prefix sum for each element in A is equal to the rank of that element in the set  $\mathcal{N}$ .

The inverse problem to the Rank problem is the Select problem:

**Definition 5** The Select problem is to maintain a set  $\mathcal{N}$  of size N with elements drawn from an ordered bounded universe  $\mathcal{M} = [0..M-1]$  and support the following operations:

```

\begin{array}{ll} \mathtt{insert}(e) & \mathcal{N} := \mathcal{N} \cup \{e\}, \\ \mathtt{delete}(e) & \mathcal{N} := \mathcal{N} \backslash \{e\}, \\ \mathtt{select}(i) & \mathit{return\ the\ element\ } e \in \mathcal{N} \ \mathit{with\ rank\ } i. \end{array}

```

These problems has been referred to as the Searchable Partial Sums problem [16, 20] when combined. Given two data structures, one used to solve the rank problem and one used to solve the select problem, we can solve the discrete extended priority queue problem. We insert and delete the given element in both data structures. To support successor(e) we first find the rank i of e and then select the element with rank i+1. To support predecessor(e) we first find the rank i of e-1 and then select the element with rank i. As noted above the last five operations of the discrete extended priority queue problem are special cases of these four operations.

Several lower bounds has been shown for the prefix sum problem. Fredman showed a  $\Omega(\lg N)$  algebraic complexity lower bound and a  $\Omega(\lg N/\lg\lg N)$  information-theoretic lower bound [10]. Yao [31] has shown that  $\Omega(\lg N/\lg\lg N)$  is an inherent lower bound under the semi-group model of computation and this was improved by Hampapuram and Fredman to  $\Omega(\lg N)$  [14].

#### 3 Summary of Included Papers

We now continue with a summary of the five included papers:

#### • Paper 1

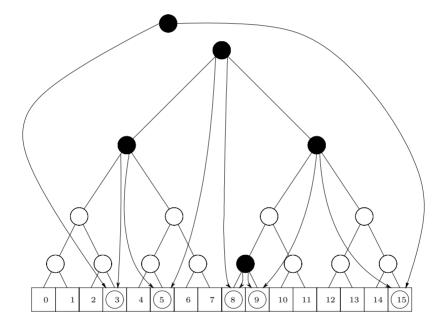

Design of a High Performance Memory Module on PC100 presents the hardware design of the special memory used in the Worst Case Constant Time Priority Queue paper (Paper 4). In this memory the words corresponds to the leaves of a balanced binary tree. Each node of the tree contains a flag bit and each such word contains the flags along the root to leaf path, so, for example, the flag at the root is in all of these words. The specific architecture was called Yggdrasil after the giant ash tree linking the worlds in Norse mythology. This particular design and hardware implementation is for the PC100 memory bus used in most Pentium-2 computers.

This thesis author's contribution to the results in this paper is the software used for the verification of the hardware implementation: a device driver, a user library, and test programs.

#### • Paper 2

In the paper Bitwise Operations under RAMBO we study the problem of computing w-bit bitwise operations using only O(1) memory probes. When using the RAM memory model there exists a  $\Omega(2^w)$  space lower bound while this space bound goes down to O(w) bits if we consider alternative memory models. We present algorithms that use four different memory models to perform bitwise boolean operations and shift operations.

#### • Paper 3

In the paper  $Multiprocess\ Time\ Queue$  we implement a time queue for elements with a bounded maximum duration C. This particular time queue supports a time-out manager controlled by two processes. The first process performs all the operations of the time queue while the other only performs  $\min$  and a restricted update.

We use a data structure similar to the Calendar Queue by Brown [7] and consider a memory model where two or more processes can share a part of the memory under mutual exclusion. The operations deleteMin and delLessThan are supported in expected constant running time under conditions that were met by our application. The other operations are supported in constant worst case running time. The space needed is proportional to the square root of the maximum duration of any element, and the number of elements, that is,  $O(\sqrt{C} + N)$ .

#### • Paper 4

The paper Worst Case Constant Time Priority Queue extends work done by Brodnik [4]. It presents a solution to the discrete extended priority queue problem using a data structure called Split Tagged Tree. A part of the data structure is stored using the Yggdrasil memory.

The solution provides all the operations in worst case constant running time using  $2M + O(\lg M)$  bits of ordinary memory and M bits of the special Yggdrasil memory. If only support for either min, deleteMin and successor or max, deleteMax and predecessor is needed the amount of ordinary memory used is reduced to  $M + O(\lg M)$  bits. The amount of ordinary memory can be reduced even further, to  $O(N \lg M)$  bits, at the expense of the worst case time. If reduced, the running time of the update operations (insert, delete, deleteMin and deleteMax) is expected constant time instead of worst case constant time.

#### • Paper 5

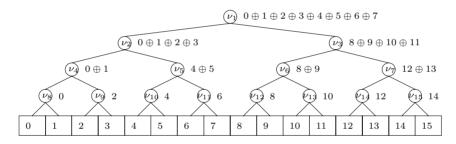

In An O(1) Solution to the Prefix Sum Problem on a Specialized Memory Architecture we study the prefix sum problem. We show that it is possible to perform both update and retrieval in O(1) time simultaneously under a memory model similar to the Yggdrasil memory model. In this variant we allow each node on the path to store several bits instead of only one bit. To

achieve the O(1) time we must allow  $O(\sqrt{M^{(\lg N)}} \cdot \lg M)$  bits of ordinary memory and  $O(N \lg M)$  bits of special memory to be used. This is a huge amount of ordinary memory and if we restrict the space requirement to be sub exponential in both N and M ( $O(\lg M)$  bits of ordinary memory and  $O(N \lg M)$  bits of special memory) we need to used  $O(\lg \lg N)$  time. This is still an improvement over the lower bounds that we side-step.

#### 4 Conclusion and Future Research

We showed that it is feasible to implement, in hardware, other memory models than the RAM memory model. We did this by implementing the Yggdrasil variant on a memory board for the PC100 memory bus. Further, we showed that, when we allow alternative memory models, it is possible solve a number of problems more efficiently than under the standard RAM memory model. We looked at two variants of priority queues; the discrete extended priority queue and the time queue; and we studied the prefix sum problem. We provided three data structures, which yield efficient solutions to these three problems. We also showed that it is possible to replace the ALU in a processor with memory while keeping the functionality provided by the ALU.

We conclude that it is possible to enhance data structures by allowing the use of alternative memory models. However, the alternative memory models seem to be different for different problems. They are therefore unlikely be an option in standard computers, which are designed to be general. Thus, we believe that it is well worth to consider alternative memory models, at least for special purpose processors.

Obviously, there is more research needed and there are a number of open research questions. We highlight a few here:

#### • Searching in Higher Dimensions.

Is it possible to use the Yggdrasil memory model (or some other novel memory model) to improve the time complexity of solutions to search problems (for example Closest Neighbour Searches) in finite d-dimensional space?

#### • Non Priority Queue Related Problems

What other problems, beside priority queue related problems, can be solved more efficiently when alternative memory models are allowed?

In this thesis we have touched on this briefly in Paper 2 where we studied the bitwise operations and how to compute them under the RAMBO model using only memory probes.

#### • Decrease Space Requirement.

– Is it possible to decrease the space requirement for the discrete extended priority queue problem to be o(M) while still retaining the

- worst case O(1) time? Brodnik and Iacono have recently started to look at this [5].

- Further, can we decrease the space requirement  $O((N^{O(1)} + M^{O(1)}) \cdot \lg M)$  bits for to the prefix sum problem while still retaining a O(1) time solution?

#### **Bibliography**

[1] M Ajtai, M Fredman, and J Komlós. Hash functions for priority queues. *Inf. Control*, 63(3):217–225, 1986.

- [2] Arne Andersson and Mikkel Thorup. Tight(er) worst-case bounds on dynamic searching and priority queues. In *Proceedings of the 32nd Annual ACM Symposium on Theory of Computing*, pages 335–342. ACM Press, May 21–23 2000.

- [3] P. Beame and F. E. Fich. Optimal bounds for the predecessor problem and related problems. *Journal of Computer and System Sciences*, 65(1):38–72, 2002.

- [4] Andrej Brodnik. Searching in Constant Time and Minimum Space (MINIMÆ RES MAGNI MOMENTI SUNT). PhD thesis, University of Waterloo, Waterloo, Ontario, Canada, 1995. (Also published as technical report CS-95-41.).

- [5] Andrej Brodnik and John Iacono. Dynamic predecessor queries. Unpublished manuscript, 2006.

- [6] Andrej Brodnik and J. Ian Munro. Neighbours on a grid. In R. Karlsson and A. Lingas, editors, SWAT '96, 5th Scandinavian Workshop on Algorithm Theory, volume 1097 of Lecture Notes in Computer Science, pages 307–320. Springer, 3–5July 1996.

- [7] Randy Brown. Calendar queues: A fast O(1) priority queue implementation for the simulation event set problem. Communications of the ACM, 31(10):1220-1227, October 1988.

- [8] Stephen A. Cook and Robert A. Reckhow. Time bounded random access machines. *Journal of Computer and System Sciences*, 7(4):354–375, 1973.

- [9] T. H. Cormen, C. E. Leiserson, and R. L. Rivest. *Introduction to Algorithms*. MIT Press and McGraw-Hill Book Company, 1990.

- [10] Michael L. Fredman. The complexity of maintaining an array and computing its partial sums. *Journal of the ACM*, 29(1):250–260, January 1982.

- [11] Michael L. Fredman and Michael E. Saks. The cell probe complexity of dynamic data structures. In *Proceedings of the 21st Annual ACM Symposium on Theory of Computing*, pages 345–354. ACM Press, May 14–17 1989.

- [12] Phillip B. Gibbons, Yossi Matias, and Vijaya Ramachandran. Can a shared-memory model serve as a bridging model for parallel computation? *Theory of Computing Systems*, 32(3):327–359, 1999.

- [13] Michael D. Godfrey. Introduction to "the first draft report on the ED-VAC" by John von Neumann. *IEEE Annals of the History of Computing*, 15(4):27–75, 1993.

- [14] Haripriyan Hampapuram and Michael L. Fredman. Optimal biweighted binary trees and the complexity of maintaining partial sums. *SIAM Journal on Computing*, 28(1):1–9, 1998.

- [15] J. Hartmanis and J. Simon. On the power of multiplication in random access machines. In 15th Annual Symposium on Switching and Automata Theory, pages 13–23, 1974.

- [16] Wing-Kai Hon, Kunihiko Sadakane, and Wing-Kin Sung. Succinct data structure for searchable partial sums. In Toshihide Ibaraki, Naoki Katoh, and Hirotaka Ono, editors, Algorithms and Computation ISAAC 2003, 14th International Symposium, volume 2906 of Lecture Notes in Computer Science, pages 505–516. Springer, December 2003.

- [17] Richard M. Karp and Vijaya Ramachandran. Parallel algorithms for shared-memory machines. In van Leeuwen [27], chapter 17, pages 869–941.

- [18] Kurt Mehlhorn, Stefan Näher, and Helmut Alt. A lower bound on the complexity of the union-split-find problem. SIAM Journal on Computing, 17(6):1093–1102, 1988.

- [19] Peter Bro Miltersen. Lower bounds for Union-Split-Find related problems on random access machines. In *Proceedings of the 26th Annual ACM Symposium on Theory of Computing*, pages 625–634. ACM Press, 23–25 May 1994.

- [20] Rajeev Raman, Venkatesh Raman, and S. Srinivasa Rao. Succinct dynamic data structure. In Algorithms and Data Structures, 7th International Workshop, volume 2125 of Lecture Notes in Computer Science, pages 426–437. Springer, 8–10 August 2001.

- [21] Arnold Schönhage. Storage modifications machines. SIAM Journal on Computing, 9(3):490–508, August 1980.

- [22] J. D. Ullman, A. V. Aho, and J. E. Hopcroft. *The Design and Analysis of Computer Algorithms*. Addison-Wesley, Reading, 1974.

- [23] L. G. Valiant. General purpose parallel architectures. In van Leeuwen [27], chapter 18, pages 943–971.

- [24] Leslie G. Valiant. A bridging model for parallel computation. *Communications of the ACM*, 38(8):103–111, August 1990.

- [25] P. van Emde Boas, R. Kaas, and E. Zijlstra. Design and implementation of an efficient priority queue. *Mathematical Systems Theory*, 10:99–127, 1977.

- [26] Peter van Emde Boas. Machine models and simulations. In van Leeuwen [27], chapter 1, pages 3–66.

[27] Jan van Leeuwen, editor. *Handbook of Theoretical Computer Science*, volume A: Algorithms and Complexity. Elsevier/MIT Press, Amsterdam, 1990.

- [28] George Varghese and Anthony Lauck. Hashed and hierarchical timing wheels: Efficient data structure for implementing a timer facility. *IEEE/ACM Transaction on Networking*, 5(6):824–834, December 1997.

- [29] John von Neumann. First draft of a report on the EDVAC. Technical report, Moore School of Electrical Engineering, University of Pennsylvania, 30 June 1945. Reprinted in [13].

- [30] A. Yao. Some complexity questions related to distributive computing. In *Proceedings of the 11th Annual ACM Symposium on Theory of Computing*, pages 209–213, 1979.

- [31] Andrew C. Yao. On the complexity of maintaining partial sums. SIAM Journal on Computing, 14(2):277–288, May 1985.

- [32] Andrew Chi-Chih Yao. Should tables be sorted? Journal of the ACM, 28(3):614–628, July 1981.

## Papers

## Paper 1

## Design of a High Performance Memory Module on PC100

#### Design of a High Performance Memory Module on PC100

Roni Leben \* Marijan Miletić <sup>†</sup> Marjan Špegel\* Andrej Trost <sup>‡</sup> Andrej Brodnik <sup>§¶</sup> Johan Karlsson<sup>¶</sup>

#### Abstract

In this contribution we present the design of a special-purpose memory board for the PC100 memory bus. The data storage on the module is placed in dynamic RAM chips and in an FPGA chip to provide for faster data access needed in increasingly popular time-critical PC applications such as real-time simulation of systems and time queue handling in general. The complexity of the PCB design for the module is one of the most demanding designs ever accomplished in Slovenia. Actually, there are just a few companies in Europe at the moment capable to design and produce the PC100-compatible boards.

The supporting software was developed under the operating system FreeBSD ver. 3.2 as a user library and a kernel module.

#### 1 Introduction and Motivation

Although many computer architectures have been proposed and implemented over the half-century of modern computing, the predominant architecture is still the von Neumann machine consisting of the processor (e.g. CPU), the memory (e.g. RAM), and the I/O units (e.g. VDU).

The communication between these units is carried out through well defined interfaces – buses. In contemporary off-the-shelf PCs one can find a variety of buses, and the most common among them are the ISA, EISA, and the PCI bus. These buses are designed to connect CPU with I/O devices (e.g. disk-, video-, network-controllers). Though the speed of communication between the CPU and I/O devices is ever increasing, it is typically still significantly lower than the speed of communication between the CPU and the main memory. In fact, because of increasingly higher requirements for the speed of the CPU-to-memory

<sup>\*</sup> Jožef Stefan Institute, Ljubljana, Slovenia

<sup>†</sup> Artinian, Ljubljana, Slovenia

<sup>&</sup>lt;sup>‡</sup>University of Ljubljana, Faculty of Electrical Engineering, Ljubljana, Slovenia

<sup>§</sup>Institute of Mathematics Physics and Mechanics, Ljubljana, Slovenia

$<sup>\</sup>P$ Luleå University of Technology, Luleå, Sweden

communication, the computer memory is typically placed on a completely different and separate bus. In the beginning of 1998, a new standard for this bus was developed and proposed by Intel called the PC100 bus, permitting speeds up to 6.4 Gbit/sec. In fact, most of creativity in computer design is nowadays spent on the interconnection between the memory and the processor, and the data throughput will ultimately depend on a number of technological and architectural decisions.

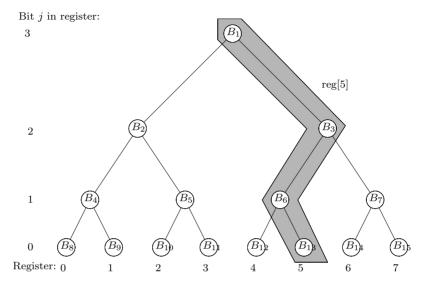

In this paper we present the design of an advanced memory module for the PC100 bus. The logical design of the module is based on a special memory topology called Yggdrasil described and tested in [4]. Briefly, the memory can be described as a binary tree where each internal node stores one bit of information. The addressable memory registers are actually at the leaves of the tree, whereas their content is stored on the path from this leaf to the root. The design of the memory is under patent protection by  $Priqueue\ AB$  from Sweden. Karlsson in his master thesis used two different implementations of the memory: the first one was software emulation of the tree in regular memory, whereas the second one was an ISA-bus hardware implementation (YGG-I), where the height of the YGG-I was 16 bits.

In the new design called YGG-II, we extended the height of YGG-I to 25 bits by splitting the address tree into two parts: the first part covering top 13 bits that were placed in an FPGA device, and the second part covering lower 12 bits that were placed in regular memory ICs. In the following section we describe the overall architecture of the YGG-II. This is followed by the description of the PCB design, and the FPGA design. We conclude the paper with the discussion of likely further work on the new module.

#### 2 YGG-II Architecture

Memory architecture of choice for the design of new PCs at the beginning of 1998 was SDRAM for the 72 bits wide PC100 bus. This is dynamic RAM with synchronous interface and clock running at 100 MHz. Internal DRAM access time of minimum 50 nsec is subdivided into several 10 nsec cycles permitting functions overlap and data bursts. Classic RAS and CAS signals for a multiplexed address and data strobe have been assigned new functions according to the simplified state diagram as shown in Fig. 6.27 in [5]. The basic timing difference is shown in Fig. 6.3 in [5].

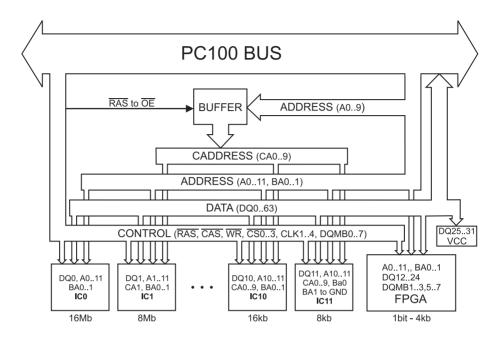

The YGG tree-like configuration, shown in Fig. 1.1, requires uniquely decreasing-capacity RAMs for each data bit. Due to the total availability of 24 address and 64 data lines, we can build two separate 25 bits high data trees. Seven MSBs are fixed to the logical 1 level by resistor's pull-up network. Active DQ24/56 flip-flops are enabled by the board-select lines, only without any addressing. The DQ23/55 data are stored in 2-bit memory controlled by the MSB A11 line. The DQ22/54 needs 4-bit memories addressed by the A10 and A11 lines at RAS time. The LSB DQ0/32 uses two SDRAM bits with all address lines active for 16MB access. Data burst length was limited to 1 in order to

Figure 1.1: Architecture of the YGG-II board.

accommodate the tree-type access rather then the forecasted long sequential order. The lower 12 data bits were realized with a  $16\mathrm{M}\times4$  SDRAM IC using only two outputs. Column addresses were sequentially reduced with RAS controlled 10-line buffer. The last IC has the BA1 bank select line grounded rather than connected to A0 as expected. That was discovered to be the way the linear addresses are generated on PC100.

The MSB SDRAM with 2×13 blocks from 4k bits downward were all squeezed into a single FPGA from the Xilinx XC4036XLA series first produced in January 1999. Only the top 12 addresses strobed by RAS are utilized, and only three of all PC100 commands need support: ACTV, READ and WRITE. The ACTV command sets FPGA RAM addresses at RAS time. Two clocks later comes CAS with WR signal deciding the remaining data transfer. The WRITE data are immediately provided whereas the READ output should appear after programmed time of 3 clock cycles. The CS0 and the CS2 signals select 16 bit words whereas the four DQMB signals enable byte operations. The CKE signal can freeze the clock, thereby extending all cycles. All of the input signals are first latched within the fast FPGA input pairs of flip-flops running at 100 MHz with less than 1.5 nsec overall clock delay. Combinatorial logic is hand-placed close to the input signals in order to achieve less than 10 nsec delay. Larger memory blocks made from 32-bit internal RAM ICs were also constrained in their relative placement within the FPGA device in order to achieve the required 100 MHz operation.

#### 3 Printed Circuit Board Design

The aforementioned YGG-II architecture was implemented on a six-layer 168-pin DIMM SDRAM format printed circuit board (PCB) module. Since our goal was to design and prototype a PC100-compliant memory module, the PCB complies with JEDEC ([3]) and Intel ([2]) specifications regarding DIMM memory modules. The printed circuit board has four signal layers and two power planes (V<sub>CC</sub> and V<sub>SS</sub>). The JEDEC standard ([3]) defines PCB width of 138.5 mm and maximum height of 38.1 mm, of which 4.0 mm are reserved for edge connector pins. Since the Xilinx XC4036XLA FPGA has a footprint of about 32 by 32 mm, there was very little room left for the connections to its pins near the edge connector pins.

But the central PCB design problem was the routing of the signals. The Intel specification ([2]) defines routing topologies, trace lengths, trace widths, clearance between traces, pads, vias, etc., maximum number of vias and layers to be used for each of about two hundred signals. On ordinary DIMM boards, the address and control lines are routed horizontally on the upper part of the PCB (if we define the lower part to be next to the edge connector) and connected to the edge connector vertically on the center of the board. The data lines are routed in vertical direction from edge connector pins via serial resistors to SDRAM IC's. The hardest restrictions, however, are placed on the four clock signals, which are routed diagonally in the two internal layers between the power planes to minimize their radiation. The edge connector pinout is designed with these restrictions in mind.

The routing topology of our design is quite different from the one mentioned above. In addition to the fourteen normal address lines, there are ten more column address lines, generated by the buffer IC. The data lines also are not routed only vertically any more; a lot of them are connected to the XC4036XLA FPGA placed on the center of the board, since the MSB bits of the tree are stored in it. Many address and control signals are also connected to the FPGA. Because of these restrictions and the deviations from the Intel's topology – as well as because of additional lines to be routed – the automatic routing performed by Specctra auto-router software package was not an easy task, and the resulting PCB fist had about 750 vias which were subsequently reduced to about 650 by hand. Some trace length restrictions also had to be loosened, because it was physically impossible to fully satisfy them. Furthermore, it did not make sense to follow the design restrictions very tightly because the internal delays of the FPGA were also not known at the time of the PCB design; namely, the FPGA internal routing was completely finished only recently. Finally, there were also many changes made to the schematic design during the design of the PCB, the so-called Engineering Change Orders (ECOs) and – since this is the first prototype – some changes were even made on the finished PCB prototypes. Because of the high design demands – as well as because of its numerous and extremely small vias, this PCB is probably also one of the most demanding designs ever accomplished in Slovenia.

#### 4 FPGA Design

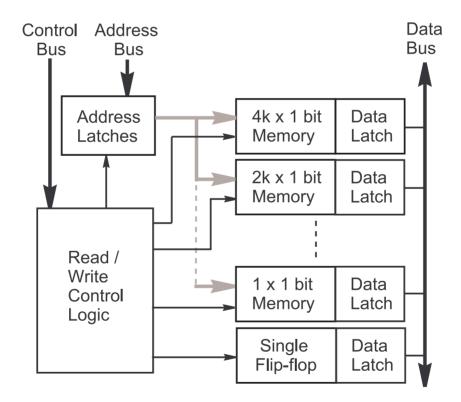

The upper part of the memory tree – as discussed before – is implemented in a Xilinx FPGA XC4036XLA consisting of 1296 Configurable Logic Blocks (CLBs). Each CLB can be used for combinatorial and registered logic or as a  $32\times1$ -bit Select-RAM static memory ( [1]). The external signals are routed through I/O Blocks (IOBs). The IOBs provide input and output latches and flip-flops used to synchronize the external signals with an internal clock. Special global-clock buffers and routing resources are used for low-skew clock distribution to each CLB and IOB.

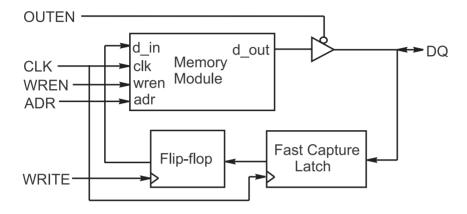

The circuit consists of 1-bit memory blocks from  $4k \times 1$ -bit to a single memory cell, of address and data latches, and of read/write control logic shown in Fig. 1.2. The control logic is used for decoding SDRAM instructions provided

Figure 1.2: The FPGA circuit architecture.

through the control bus signals. The implemented instructions are ACTV (RAS cycle), READ and WRITE. Since the upper memory tree uses only row-address lines, all the internal address signals are latched during ACTV command. The

timing diagram of the READ and WRITE instructions was determined from the SDRAM specifications. The detail structure of one memory block is presented in Fig. 1.3. During the execution of the READ instruction, the data is trans-

Figure 1.3: A detail of one memory block.

ferred from the output of the memory module through the 3-state output buffer in the third cycle after the instruction. The data and the WRITE instruction are inserted simultaneously in the write cycle and are latched in the fast capture latches in the IOBs. The fast capture latches are used to meet SDRAM set-up and hold-time requirements as described in [6]. After decoding of the WRITE instruction, each data bit is captured in a single flip-flop for subsequent transfer to the memory module during the following clock cycles.

The circuit was designed schematically with the Xilinx Foundation package. which provides many already prepared logic blocks and a hardware macro generator. The macro generator is useful for quick composition of different memory modules but is unfortunately limited to the memory depth of 256 locations only. Larger memory modules were designed hierarchically from the basic  $32\times1$ -bit synchronous Select-RAM. We extensively used relationally placed macros for manual mapping of Select-RAM cells and decode logic in 2 column wide CLB matrices. Select-RAM data outputs were combined using 3-state buffers, which are faster than combinatorial multiplexers. The critical part of the design is the read/write control logic required to operate at 100MHz clock frequency. The logic was manually mapped and some parts were placed to absolute CLB locations inside FPGA. The best locations for the control logic were derived experimentally after many automatic placement and routing iterations. The delay-driven placement and routing was used, based on timing specifications for the critical paths in the design. The complete design took several months due to many design iterations, hand mapping and placements, as well as due to very long compilation times permitting only one or two routing iterations per day.

#### 5 Conclusions

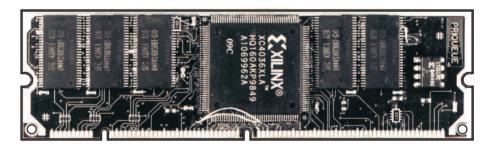

In this contribution we presented an architecture and design of a highly advanced memory board for the PC100 memory bus. The board was designed, produced and fully tested in Slovenia. The tests show that the board performs according to the specifications of this bus and hence allows accesses without wait-states, which in other words means, that it supports the same access speed as ordinary DRAM boards.

The successful development and prototyping of our memory module proves two things: first, the feasibility of the tree topology of RAM and consecutively its usefulness in, for example, real-time applications which involve efficient handling of time-queues. Second, our design team has clearly demonstrated sufficient expertise and resources to create this sophisticated piece of electronic hardware and, therefore, seems well qualified for competing on international markets without hesitation.

#### Acknowledgments

We would like to thank *Jerovšek Computers* for a computer that was used for testing the board (cf. Fig. 1.4) in a real environment.

Figure 1.4: Picture of a working prototype.

#### References

- [1] Xilinx Inc. XC4000XLA/XV field programmable gate arrays, product specification, May 1999.

- [2] INTEL. Pc sdram unbuffered dimm specification, February 1998. Revision 1.0.

- [3] JEDEC. Mo-161 multiple keyways dimm standard, August 1998. Issue C.

- [4] J. Karlsson. Evaluation of different solutions to the left-right-neighbour and priority queue problems, June 1998.

- [5] B. Price. High Performance Memories. John Wiley & Sons, England, 1996.

- [6] B. Taylor. XC4000XL FPGAs interface to SDRAMs at 100MHz, Xcell, Q2, 1998.

## Paper 2

# Bitwise Operations under RAMBO

### Bitwise Operations under RAMBO

Andrej Brodnik \*†‡ andrej.brodnik@upr.si

Johan Karlsson\* johan.karlsson@csee.ltu.se

#### Abstract

In this paper we study the problem of computing w-bit bitwise operations using only O(1) memory probes. We show that under the RAM model there exists a  $\Omega(2^w)$  space lower bound while under the RAMBO model this space bound goes down to O(w) bits. We present algorithms that use four different RAMBO memory topologies to perform bitwise boolean operations and shift operations.

### 1 Introduction

A computer today consists of a CPU, memory, and an I/O subsystem. The CPU contains, at least, a control unit, a cache, and an Arithmetic Logic Unit (ALU). The ALU is used to, given operands and an operation code (opCode), compute various functions. These functions include the bitwise operations (boolean operations and various shifts) and arithmetic operations (addition, subtraction, multiplication, and division). Although the arithmetic operations are considered atomic operations, they still consist of several micro-steps which, in turn, usually are bitwise operations (for more details see any text book on computer architectures, e.g. [10]).

In theoretical computer science we model such a computer as a RAM (cf. [5, 18]) where the processor is capable of performing functions from some predefined finite subset of  $NC^1$  in O(1) time. The class  $NC^k$  of functions is defined by:

**Definition 2.1** [11, p. 135] For each  $k \geq 0$  the class  $NC^k$  consists of the search problems solvable by log-space uniform classes of boolean circuits having polynomial size and depth  $O(\log^k w)$

$NC^1$  involves circuits of logarithmic depth that computes, at each step, various bitwise operations (compare micro-steps above). Indeed, these operations could be computed using table lookup – i.e. the circuit elements would be replaced by memory probes only. However, the size of such table would become prohibitively large. In this paper we use a variant of the RAM model called

<sup>\*</sup>Luleå University of Technology, Sweden

<sup>&</sup>lt;sup>†</sup>University of Primorska, Slovenia

<sup>&</sup>lt;sup>‡</sup>Institute of Mathematics, Physics, and Mechanics, Slovenia

RAMBO (RAM with bytes/bits overlapping) and show that all bitwise operations can be performed using writes and reads of memory only, while the space requirement remains at a bearable O(w) bits.

As said, we can divide the bitwise operations into shifts and boolean operations. Further, the shifts come in five flavors: left and right shift, left and right rotation, and arithmetic right shift. In Sect. 2 we show how all these operations can be performed using 4w bits under the RAMBO model – a clear gain over the straightforward approach which uses  $O(2^w w^2)$  bits under the RAM model. On the other hand, to implement the boolean operations using table lookup, although they all can be computed using NAND (or NOR) only, requires at least  $\Omega(2^w)$  bits (see Corollary 2.1) of memory under the RAM model and a straightforward approach uses  $O(2^{2w}w)$  bits. This is much more than O(w) bits needed under the RAMBO model as will be seen in Sect. 3. In total, we reduce the size of the data structure (i.e. program) from  $O(2^{2w}w)$  under the RAM model to O(w) under the RAMBO model without increasing the time complexity.

Finally in Sect. 4 we show how the presented operations can be combined into a function to perform addition of two words in  $O(\lg w)$  steps and O(w) space under the RAMBO model.

### 1.1 Preliminaries

The RAM model models a computer as a CPU and an infinite set of memory registers [5, 18]. There are several variants of the RAM model (e.g., MBRAM [18], and  $AC^0$  RAM [2]) and they differ in which operations the CPU can perform in unit time. Also they differ in whether the memory registers are of bounded size or not. In this paper we consider a variant of the RAM model where the only operations are read and write from/to memory with registers of bounded size w (cf., cell probe model [20]). We refer to this variant as the *Read-Write RAM* model.

A Read-Write RAM corresponds to a Turing Machine (TM) [18] with an alphabet of size  $2^w$  ([0,1,..., $2^w-1$ ]), and the possibility to access a random tape location in unit time. The state transition function (the program) of the TM corresponds to precomputed tables in the RAM. The computation of some functions requires a large lookup table:

**Theorem 2.1** The computation of an onto function  $f : A \to \mathcal{B}$  on a Read-Write RAM requires a lookup table of size  $\Omega(B)$ , where B is the size of  $\mathcal{B}$ .

**Proof:** To compute f, a TM needs to be able to write all characters in the range  $\mathcal{B}$ . A TM uses a tuple in its program to decide what to write and hence the TM needs at least B tuples in the program. Hence, the size of the lookup table under the Read-Write RAM is at least B.

QED

When considering a character from the alphabet as a binary number the lower bound for performing bitwise boolean operations on such a character under the Read-Write RAM model, is:

Corollary 2.1 A Read-Write RAM requires a lookup table of size  $\Omega(2^w)$  to perform bitwise boolean operations.

**Proof:** The range of the boolean operations is the whole alphabet, which is of size  $2^w$ . Hence, from Theorem 2.1 we know that the size of the lookup table under the Read-Write RAM is  $\Omega(2^w)$ .

We use the term register when referring to a specific memory location storing a word and the term word to denote a w-bit value. The notation  $W_i$  is used to denote the ith bit of the word/register W, where  $0 \le i < w$ . The least significant bit of a word/register is bit 0 while the most significant bit is bit w-1. When depicting a word/register we place the most significant bit to the left. Hence, in the 8-bit word abcdefgh, a is the most significant bit 7 while h is the least significant bit 0. We let ONE denote the w-bit word consisting of w ones (1..1), and ZERO denote the w-bit word consisting of w zeros (0..0).

In the RAM model all the bits are unique for all registers. The RAMBO model is an extended RAM model which also has a part of memory where a bit may occur in several registers or in several positions in one register. The way the bits occur in this part of the memory has to be specified as part of the model. If a bit occurs in more than one position in a register (it is overlapped), and different values are written to the bit, then the bit will store an arbitrary value.

The RAMBO model was suggested by Fredman and Saks [7], and further described by Brodnik [3]. One variant called *Yggdrasil* was used by Brodnik et al. to achieve a worst case constant time priority queue [4]. In this paper we use several variants of the RAMBO model.

The problem of performing boolean operations in different models of computations has been studied extensively. Rennard describes how to perform the boolean operations in the Game of Life model [15]. Shamir describes a paradigm called visual computation in which he shows that the boolean operations can be computed [16]. Ogihara et al. show how to simulate and or circuits on a DNA computer [14], while Ahrabian et al. simulate nand circuits [1]. Tsai et al. derive a systematic algorithm for constructing quantum boolean circuits [17]. The reason to consider the boolean operations is that arithmetic operations, e.g. addition, multiplication and so on, can be computed, using only them, in  $O(w^{O(1)})$  time and no additional space.

### 2 Shift and Rotation Operations

In this section we introduce three new variants of RAMBO (*Line*, *Tail*, and *Circle*) and use them to implement shift and rotation operations. In all examples in this section we assume that w = 8 and x=abcdefgh.

### 2.1 Shift

To shift the bits of a word we use the *Line* variant of RAMBO. Line consists of 2w bits used to store w + 1 registers of size w bits. We label the bits  $\lambda_i$ , where

$0 \le i < 2w$ . To store bit j of register line [l] we use bit  $\lambda_i$ , where i = j + l.

As an example, let us write ZERO to line[8] and afterwards write x to line[0]. Then  $\lambda_{15}=\lambda_{14}=\ldots=\lambda_9=\lambda_8=0$ ,  $\lambda_7=a$ ,  $\lambda_6=b,\ldots,\lambda_1=g$ , and  $\lambda_0=h$ . Now, since register line[3] consists of  $\lambda_{10}\lambda_9\lambda_8\lambda_7\lambda_6\lambda_5\lambda_4\lambda_3$ , i.e. 000abcde, reading this register gives the same result as right shift of x three steps. In general, reading register line[ $\delta$ ] gives the result of right shift  $\delta$  steps. Similarly, after initializing line[0] with ZERO, writing x to register line[ $\delta$ ] and reading line[0] gives us the result as if x is shifted left  $\delta$  steps (cf. Alg. 2.1). Hence,

**Lemma 2.1** We can perform both left and right shifts using 3 probes and 2w bits.

### 2.2 Arithmetic Shift

To perform arithmetic right shift of a word we use the Tail variant of RAMBO. This variant uses w bits to store w registers of size w bits. We label the bits  $\theta_i$ , where  $0 \le i < w$ . To store bit j of register tail[l] we use bit  $\theta_i$ , where i = min(j + l, w - 1).

In this example we write x to tail[0], then  $\theta_7 = a$ ,  $\theta_6 = b$ , ...,  $\theta_1 = g$ , and  $\theta_0 = h$ . Now, since register tail[3] consists of  $\theta_7\theta_7\theta_7\theta_6\theta_5\theta_4\theta_3$ , i.e. aaaabcde, reading this register gives the same result as arithmetic right shift three steps. In general, reading register tail[ $\delta$ ] gives the result of arithmetic right shift  $\delta$  steps (cf. Alg. 2.1). Hence,

**Lemma 2.2** We can perform arithmetic right shift using 2 probes and w bits.

#### 2.3 Rotation

Rotation (also known as barrel shift) takes the bits which have been shifted out at one end and shifts them in on the other end. To perform rotations we use the Circle variant of RAMBO which uses w bits to store w registers of size w. We label the bits  $\varsigma_i$ , where  $0 \le i < w$ . To store bit j of register circle[l] we use bit  $\varsigma_i$ , where  $i = (j + l) \mod w$ .

Again, when we write x to circle[0], then  $\varsigma_7 = a$ ,  $\varsigma_6 = b$ , ...,  $\varsigma_1 = g$ , and  $\varsigma_0 = h$ . Since register circle[3] consists of  $\varsigma_2\varsigma_1\varsigma_0\varsigma_7\varsigma_6\varsigma_5\varsigma_4\varsigma_3$  reading it gives the same result as right rotation of x three steps. In general, reading register circle[ $\delta$ ] gives the result of right rotation  $\delta$  steps (cf. Alg. 2.1). Further, writing the word to register circle[ $\delta$ ] and reading circle[0] gives the same result as left rotation  $\delta$ . Hence,

**Lemma 2.3** We can perform both left and right rotations using 2 probes and w bits.

The three lemmata above give us:

**Theorem 2.2** We can perform any of the five shifting operations using 4w bits in at most 3 probes.

```

word shiftRight(word a, int \delta) line[w] = ZERO; line[0] = a; return line[\delta]; word shiftLeft(word a, int \delta) line[0] = ZERO; line[\delta] = a; return line[0]; word arithShiftRight(word a, int \delta) tail[0] = a; return tail[\delta]; word rotateRight(word a, int \delta) circle[0] = a; return circle[\delta]; word rotateLeft(word a, int \delta) circle[\delta] = a; return circle[0];

```

**Algorithm 2.1:** Methods to compute right and left shift, arithmetic right shift and right and left rotation  $\delta$  steps of a.

### 3 Boolean Operations

We continue with the boolean operations starting with 1-bit values and then generalize to w-bit values. Furthermore, we show how to, simultaneously, perform different boolean operations on the w-bit arguments.

We assume that the reader is familiar with the 16 different boolean operations on two arguments a and b, where  $a, b \in \{0, 1\}$  (cf., any textbook on the subject, e.g., "Discrete and Combinatorial Mathematics" [8]).

### 3.1 Simple Boolean Operations

To describe how to compute the boolean operation we use constants  $\mathcal{C} = \{\mathcal{Z}, \mathcal{O}, \mathcal{A}, \mathcal{B}\}$  as indices into a table  $\mathtt{val}[|\mathcal{C}|]$ . The table is used to store constants  $\mathtt{val}[\mathcal{Z}]=\mathtt{ZERO}$ ,  $\mathtt{val}[\mathcal{O}]=\mathtt{ONE}$  and values  $\mathtt{val}[\mathcal{A}]=\mathtt{a}$ ,  $\mathtt{val}[\mathcal{B}]=\mathtt{b}$ . We also have an array  $\mathtt{r}[\mathtt{2}]$  to store two 1-bit values. The values from  $\mathtt{val}$  are used both as indices into and as values of  $\mathtt{r}$ . At the end  $\mathtt{r}$  also contains the result of our operation. We compute a given boolean operation by three writes (call them steps) into  $\mathtt{r}$  and finally read the result from  $\mathtt{r}$ .

As an example, let us compute a AND b. We want to find the result in r[0]. The result should be 1 if neither a nor b are 0. Hence, we initialize r[0] with 1,

$$r[0] = 1 (1)$$

then we write 0 to r[0] if a == 0 or b == 0. Instead of checking if a == 0 we can just write 0 to r[val[A]],

$$r[a] = 0 (2)$$

since if a == 1 we will write 0 to r[1] which does not affect our result. Similarly for b,

$$r[b] = 0 . (3)$$

Finally, register r[0], contains a 0 if either or both of a and b were 0 and 1 otherwise,

$$r[0] \rightarrow res$$

. (4)

On the other hand, when computing a NOR b, we initialize r[1] with 1, and write 0 to both r[val[A]] and r[val[B]]. Then if neither a nor b are 1, r[1] will still contain 1 and 0 otherwise.

It turns out that all 16 boolean operations can be computed in the same way where the index of  $\mathbf{r}$  and the value stored into  $\mathbf{r}$  at each step depends only on the opCode of the boolean operation. A function  $f_{i,j}$  (opCode) can be used to decide which value to write into which register (cf. Alg. 2.2). The

```

bool boolOp(int opCode, bool a, bool b)  \text{val}[\mathcal{A}] = \text{a; val}[\mathcal{B}] = \text{b;}   \text{r}[\text{val}[f_{1,1}(\text{opCode})]] = \text{val}[f_{1,2}(\text{opCode})];   \text{r}[\text{val}[f_{2,1}(\text{opCode})]] = \text{val}[f_{2,2}(\text{opCode})];   \text{r}[\text{val}[f_{3,1}(\text{opCode})]] = \text{val}[f_{3,2}(\text{opCode})];   \text{return r}[\text{val}[f_{1,1}(\text{opCode})]];

```

Algorithm 2.2: Method to compute any boolean operation.

function  $f_{i,j}$  (opCode) can be tabulated using a table F[opCode][i][j], where we, for the sake of simplicity, let indices into the table F (and its variants we will introduce later) always start at 1 (cf. Alg. 2.3 and Alg. 2.4). The second line in F, for example, corresponds to the and operation (i.e. the opCode of and is 2), where  $\{\mathcal{Z}, \mathcal{O}\}$  means write val[ $\mathcal{O}$ ] to r[val[ $\mathcal{Z}$ ]] (i.e., r[ZERO]=ONE) etc., which matches Eq. 1 – 3.

The size of table F is  $\langle \#$  of boolean operations $\rangle \cdot \langle \#$  of steps $\rangle \cdot 2 \cdot \lg |\mathcal{C}| = 192$  bits. Hence, bool0p in Alg. 2.4 computes any 1-bit boolean operation, in 34 memory probes (reads or writes), using 198 bits (besides F, the arrays val and r use 6 bits). As we shall see later, we can compress the table F to 96 bits which totals to 102 bits over all. Hence, we conclude with:

**Lemma 2.4** We can compute any boolean operation using 102 bits of memory using O(1) reads and writes only.

This is worse than the 64 bits straighforward table lookup algorithm under the RAM model. But in the next section we build on this and get a solution for w-bit words.

### 3.2 w-bit Bitwise Boolean Operations

To compute w-bit bitwise boolean operations we use a variant of the RAMBO model which we refer to as Twin. It consists of 2w bits labeled  $\tau_{i,j}$  where  $0 \le i < w$  and  $j \in \{0,1\}$  (see Fig. 2.1). Although there are only 2w bits in Twin, they represent  $2^w$  registers. The register at address  $a_{w-1}a_{w-2}\dots a_0$  (denoted  $twin[a_{w-1}a_{w-2}\dots a_0]$ ) is stored using the bits  $\tau_{w-1,a_{w-1}}\tau_{w-2,a_{w-2}}\dots\tau_{0,a_0}$ , i.e.,

```

int F[opCode][i][j] = {

\{\{\mathcal{Z}, \mathcal{Z}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* 0 */

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* \text{ a AND b }*/

\{\{\mathcal{Z}, \mathcal{Z}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* NOT (a IMPLIES b) */

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* \ a */

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* \text{ NOT (b IMPLIES a) }*/

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* b */

\{\{\mathcal{Z}, \mathcal{Z}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* \text{ a xor b }*/

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* \text{ a OR b }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* \text{ a NOR b }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* \text{ a xnor b }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{Z}\}\}, /* \text{ NOT b }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{A}\}\}, /* \text{ b implies a }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{Z}, \mathcal{Z}\}\}, /* \text{ NOT a */}

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{Z}\}, \{\mathcal{B}, \mathcal{O}\}\}, /* \text{ a implies b }*/

\{\{\mathcal{Z}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{O}\}\}, /* \text{ a NAND b }*/

\{\{\mathcal{O}, \mathcal{O}\}, \{\mathcal{A}, \mathcal{O}\}, \{\mathcal{B}, \mathcal{O}\}\} /* 1 */ \}

```

Algorithm 2.3: Table F used by boolOp in Alg. 2.4.

```

bool boolOp(int opCode, bool a, bool b)

val[A] = a; val[B] = b;

r[val[F[opCode][1][1]]] = val[F[opCode][1][2]];

r[val[F[opCode][2][1]]] = val[F[opCode][2][2]];

r[val[F[opCode][3][1]]] = val[F[opCode][3][2]];

return r[val[F[opCode][1][1]]];

```

**Algorithm 2.4:** Method to compute any boolean operation using table lookup.

the *i*th bit of twin  $[a_{w-1}a_{w-2}...a_0]$  is  $\tau_{i,a_i}$  For example, twin [0011] consists of the bits  $\tau_{3,0}\tau_{2,0}\tau_{1,1}\tau_{0,1}$ .

| bit: | 3           | 2           | 1           | 0           |  |

|------|-------------|-------------|-------------|-------------|--|

|      | $	au_{3,1}$ | $	au_{2,1}$ | $	au_{1,1}$ | $	au_{0,1}$ |  |

|      | $	au_{3,0}$ | $	au_{2,0}$ | $	au_{1,0}$ | $	au_{0,0}$ |  |

Figure 2.1: Twin memory with 4-bit words (w = 4)

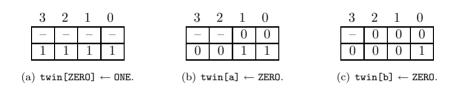

To get a better feeling for how this memory behaves, let us assume that all bits in the memory are zero (Fig. 2(a)). Then we write 1111 to twin[0101] (Fig. 2(b)). Now, if we read twin[0011] we get the word 1001, and twin[1100] gives 0110.

The twin registers behave as w parallel arrays r. Hence, similarly to the computation of AND above, if we want to compute a AND b with w-bit registers, we first write  $val[\mathcal{O}]$  to  $twin[val[\mathcal{Z}]]$ , then we write  $val[\mathcal{Z}]$  to both

Figure 2.2: Twin example with w = 4.

twin[val[ $\mathcal{A}$ ]] and twin[val[ $\mathcal{B}$ ]]. As an example (Fig. 2.3) we use a=0011, and b=0101 and study the content of twin[val[ $\mathcal{Z}$ ]]. After the three writes, register twin[val[ $\mathcal{Z}$ ]] (Fig. 3(c)) contains 0001 which is the result of bitwise boolean AND of 0011 and 0101.

Figure 2.3: Computation of a AND b using Twin where a=0011, and b=0101

The special registers twin in the Twin RAMBO variant lets us use a method similar to boolOp (Alg. 2.4) to compute bitwise boolean operations on w-bit words. We are still using F from Alg. 2.3 but the parameters  ${\tt a}$  and  ${\tt b}$  and the array val are w bits wide. Further, the array  ${\tt r}$  is replaced by the twin registers. Hence using 4w+192 bits of regular memory and 2w bits of RAMBO memory we can compute any of the boolean operations.

As stated above, we can reduce the amount of memory needed by compressing the table F. The first, second, and fourth columns only consist of the values  $\mathcal{Z}$  and  $\mathcal{O}$  and hence only 1 bit for each position is needed. The third column always contains  $\mathcal{A}$  and it can be removed entirely. The value in the fifth column is either  $\mathcal{Z}$  or  $\mathcal{B}$  and needs only 1 bit. The value in the sixth column is either  $\mathcal{Z}$ ,  $\mathcal{O}$ , or  $\mathcal{A}$  and to store such a value we need 1.5 bits. Hence, each row in the table actually only needs 5.5 bit instead of 12 bit which totals to 88 bits for the table. However, we use 2 bits (actually 2 1-bit values) to store the last column, in order to avoid the gory details needed to use only 1.5 bits, which totals to 96 bits for the table. A new table Fc stores in columns 1, 2, and 3 the values from column 1, 2, and 4 of F respectively. The fourth column stores  $\mathcal{Z}$  if the value of the fifth column of F is  $\mathcal{Z}$  and  $\mathcal{O}$  if it is  $\mathcal{B}$ . The fifth column stores  $\mathcal{O}$  if the sixth column of F is  $\mathcal{A}$  and  $\mathcal{Z}$  otherwise. The sixth columns stores  $\mathcal{O}$  if the sixth column of F is  $\mathcal{A}$  and  $\mathcal{Z}$  otherwise.

To be able to use the table Fc we need to compute the values stored in

the fifth and sixth column of table F based on table Fc. To get the value from column five of F we first write ZERO to twin[ONE], then we write b to twin[val[Fc[opCode][4]]]. Now if Fc[opCode][4] was  $\mathcal{O}$ , twin[ONE] will contain b and ZERO otherwise. We store this value in a variable, d, and use it where column five of F was used. We compute the value stored in the sixth column of F in a similar way and store it in variable, e, for later use. Since Fc only stores the values  $\mathcal{Z}$  and  $\mathcal{O}$ , the table val only need to store two w-bit values (ZERO and ONE). However, the two variables d and e are also w-bit values. This gives us:

**Theorem 2.3** We can compute any bitwise boolean operation on w-bit words in 36 memory probes using 4w+96 bits of regular memory and 2w bits of RAMBO memory in O(1) time.

This is a huge improvement over the  $\Omega(2^w)$  bits needed for table lookup under RAM.

The number of memory probes needed can be reduced by using more memory. Since, Fc is storing just the indices  $\mathcal Z$  and  $\mathcal O$ , we can avoid one level of indirection and the usage of the array val, by storing ZERO and ONE directly into a table Fw, e.g., the and row is {ZERO, ONE, ZERO, ONE, ZERO, ZERO}. This increases the total usage of regular memory to 96w+2w bits, but we only need 29 memory probes (cf. Alg. 2.5) which gives us the following result:

**Corollary 2.2** We can compute any bitwise boolean operation on w-bit words in 29 memory probes using 96w + 2w bits of regular memory and 2w bits of RAMBO memory in O(1) time.

Again, this is still a large improvement over the  $\Omega(2^w)$  bits needed for table lookup under RAM.

Note that for 1-bit words the total amount of memory is 100 bits of regular memory and no bits of RAMBO memory (r is used instead of twin) which is a slight improvement over the result in Sect. 3.1.

```

word boolOp(int opCode, word a, word b)

twin[ONE] = ZERO; twin[Fw[opCode] [4]] = b; d = twin[ONE];

twin[ONE] = ZERO; twin[Fw[opCode] [5]] = ONE;

twin[Fw[opCode] [6]] = a; e = twin[ONE];

twin[Fw[opCode] [1]] = Fw[opCode] [2];

twin[a] = Fw[opCode] [3];

twin[d] = e;

return twin[Fw[opCode] [1]];

```

**Algorithm 2.5:** Method to compute any combination of bitwise boolean operations for w-bit arguments.

Moreover, when storing w-bit values in the table Fw we can actually decide which operation we want to perform on individual bits by storing other values

than ZERO and ONE. For example, we can perform, xor on the bits at even position and AND on the bits at odd positions (xor-AND).

As an example, we compute, in 2-bit words, xor for the least significant bit and AND for the most significant bit. The row for this operation in the table Fw would be {00, 10, 01, 11, 00, 01}. The most significant bit in each word corresponds to the values in the AND line of Fc and the least significant bit to the values in the xor line. If we let a=11 and b=00 the result should be 01. Following the steps in Alg. 2.5 with these values we get the program trace in Fig. 2.4, which gives the expected result.

| Instruction                            | $\tau_{1,1}\tau_{0,1}/\tau_{1,0}\tau_{0,0}$ | d  | e  |

|----------------------------------------|---------------------------------------------|----|----|

| twin[11] = 00                          | 00/                                         | _  | _  |

| twin[11] = 00                          | 00/                                         | -  | -  |

| d = twin[11]                           | 00/                                         | 00 | -  |

| twin[11] = 00                          | 00/                                         | 00 | -  |

| twin[00] = 11                          | 00/11                                       | 00 | -  |

| twin[01] = 11                          | 01/11                                       | 00 | -  |

| e = twin[11]                           | 01/01                                       | 00 | 01 |

| twin[00] = 10                          | 01/10                                       | 00 | 01 |

| twin[11] = 01                          | 01/11                                       | 00 | 01 |

| twin[d] = e                            | 01/01                                       | 00 | 01 |

| $\texttt{twin[00]}  \to  \texttt{res}$ |                                             |    |    |

Figure 2.4: Trace of boolOp in Alg. 2.5 with a=11, b=00, and Fw[opcode] = {00,10,01,11,00,01}.

Hence, we can support any combination of bitwise boolean operations on individual bits in w-bit words using 6w extra bits per combination. Let c be the number of combinations of different boolean operations we wish to support (note  $c \le 16^w$ ). Then,

**Corollary 2.3** We can compute, in O(1) time, any of c combinations of bitwise boolean operations on individual bits in w-bit words in 29 memory probes using  $c \cdot 6w + 2w$  bits of regular memory and 2w bits of RAMBO memory.

### 4 Addition Operation

Finally, as an example of how to use these bitwise operations we implement addition of two words within our model of computation. When implementing addition in hardware the depth of the circuit has to be at least  $\Omega(\log_d w)$  if the fan-in is restricted to d. Addition is in  $NC^1$  [12] and we match the lower bound using the procedure used by Cormen et al. [6, Sect. 29.2.2].

The basic idea is to use a parallel prefix circuit to compute all the carry bits, c, first and then finally the sum is computed as the parity of a, b and c (boolOp(XOR, c, boolOp(XOR, a, b))).

The carry bit  $c_i$  depends on  $a_{i-1}$ ,  $b_{i-1}$  and maybe  $c_{i-1}$ . If  $a_{i-1} = b_{i-1} = 0$  then  $c_i = 0$  (we kill the carry bit), if  $a_{i-1} = b_{i-1} = 1$  then  $c_i = 1$  (we generate the carry bit), and if  $a_{i-1} \neq b_{i-1}$  then  $c_i = c_{i-1}$  (we propagate the carry bit).

The notation of *carry status* (kill (k), generate (g), and propagate (p)) is used by Cormen et al. and we can compute combined carry status of two consecutive full adders using the carry status operator  $\otimes$ . The combined carry status is propagate if both the operands are propagate, it is generate if either the second operand is generate or the first is generate and the second is propagate, and otherwise it is kill.

We encode the three values of the carry status  $\mathbf{x}_i$  using two bits (k = 00, p = 01, g = 10). Using this encoding it is easy to compute  $\mathbf{x}_i$  since  $\mathbf{x}_{i_0} = \mathbf{a}_i \, \mathtt{XOR} \, \mathbf{b}_i$  and  $\mathbf{x}_{i_1} = \mathbf{a}_i \, \mathtt{AND} \, \mathbf{b}_i$ . Note, that we can compute both bits, in spite of the fact that we deal with two different boolean operations, simultaneously as shown in Fig. 2.4. Furthermore, we can do this simultaneously for all i.

As shown by Cormen et al. [6] the rest of the algorithm uses  $O(\lg w)$  boolean operations and shifts. We leave the details of the implementation to the reader.

### 5 Conclusion

The computation of the bitwise operations under the RAM model using O(1) table lookups requires a table of size  $\Omega(2^w)$  while we have presented a solution under the RAMBO model using only O(w) space still using only O(1) table lookups. To support all the bitwise operations we used 4w + 96 bits of regular memory and 6w bits of special RAMBO memory.

Furthermore, we also showed how to support simultaneous combinations of boolean operations using 6w additional bits of ordinary memory per combination. To implement addition we took advantage of the combined boolean operations and got a  $O(\lg w)$  time solution.

To perform the bitwise operations we introduced four new variants of the RAMBO model which are straightforward to implement in hardware. For a discussion on how to implement new variants of the RAMBO model we refer the interested reader to "Design of High Performance Memory Module on PC100" by Leben et al. [13].

The address decoding for memory under the RAM model is in  $NC^1$  but not in  $NC^0$ . The address decoding for the twin memory is in  $NC^0$  while the address decodings for line, tail and circle are in  $NC^1$ .

Content-addressable memory (CAM) (also known as associative memory) [9] is another technique where the memory structure is modified. CAM requires additional hardware to handle processing of all memory cells in parallel. The RAMBO variants, on the other hand, only requires modifications to the address decoding.

### Acknowledgment

The authors would like to thanks Prof. Svante Carlsson who participated in initial discussions.

### References

- [1] H. Ahrabian and A. Nowzari-Dalini. DNA simulation of nand boolean circuits. *The Electronic International Journal Advanced Modeling and Optimization*, 6(2):33–41, 2004.

- [2] Arne Andersson, Peter Bro Miltersen, Soren Riis, and Mikkel Thorup. Static dictionaries on  $AC^0$  RAMs: Query time  $\Theta(\sqrt{\log n/\log\log n})$  is necessary and sufficient. In 37th Annual Symposium on Foundations of Computer Science (FOCS), pages 441–450. IEEE Computer Society, 14–16 October 1996.

- [3] Andrej Brodnik. Searching in Constant Time and Minimum Space (MINIMÆ RES MAGNI MOMENTI SUNT). PhD thesis, University of Waterloo, Waterloo, Ontario, Canada, 1995. (Also published as technical report CS-95-41.).

- [4] Andrej Brodnik, Svante Carlsson, Michael L. Fredman, Johan Karlsson, and J. Ian Munro. Worst case constant time priority queue. *Journal of System and Software*, 78(3):249–256, December 2005.

- [5] Stephen A. Cook and Robert A. Reckhow. Time bounded random access machines. *Journal of Computer and System Sciences*, 7(4):354–375, 1973.

- [6] T. H. Cormen, C. E. Leiserson, and R. L. Rivest. *Introduction to Algorithms*. MIT Press and McGraw-Hill Book Company, 1990.